### **ChipGlobe Company Overview – 11.02.2023**

ChipGlobe GmbH Volker Frisch, CEO

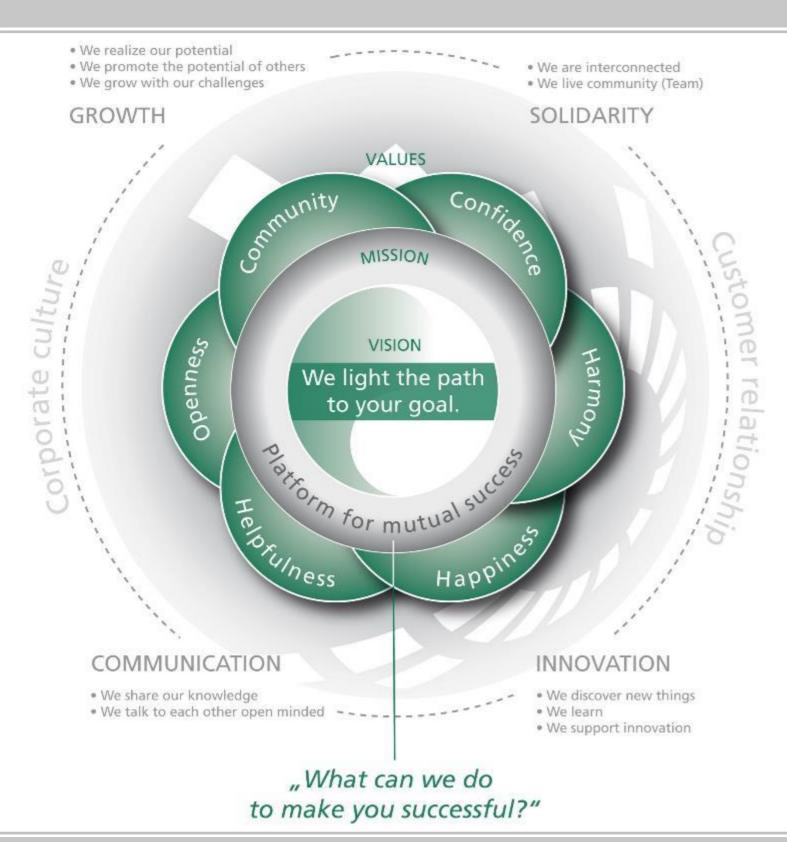

### Our Identity - Vision, Mission, Values, Company

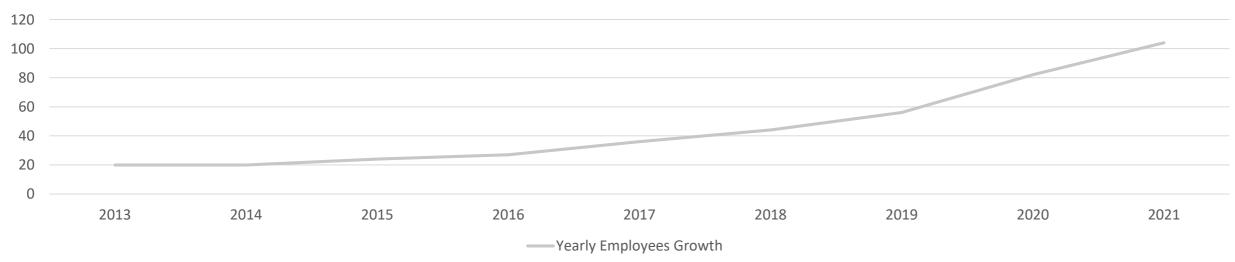

# ChipGlobe in a nutshell

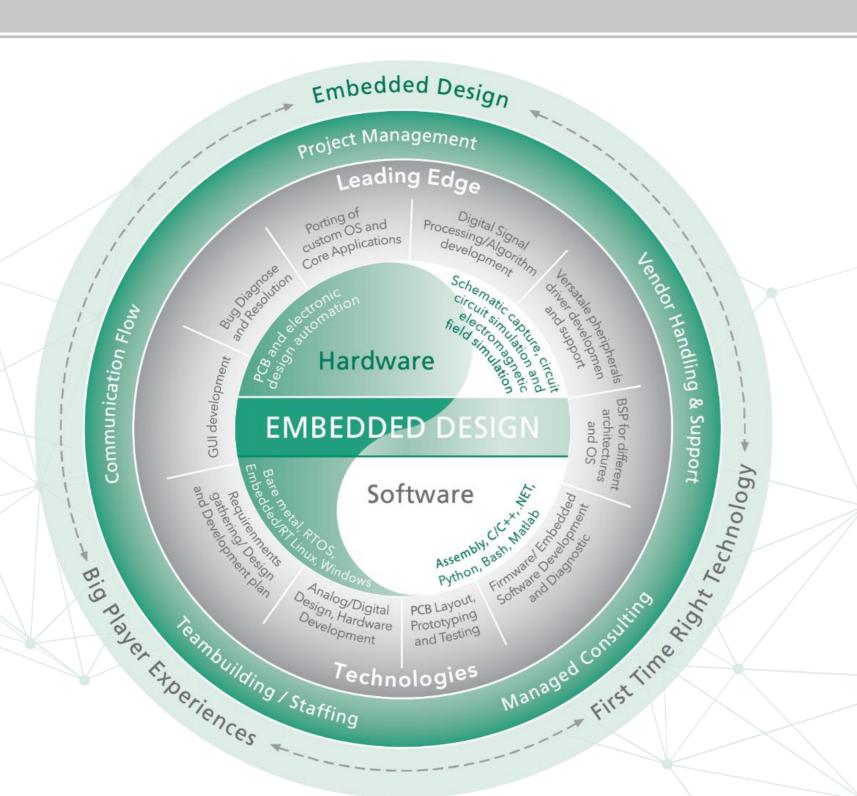

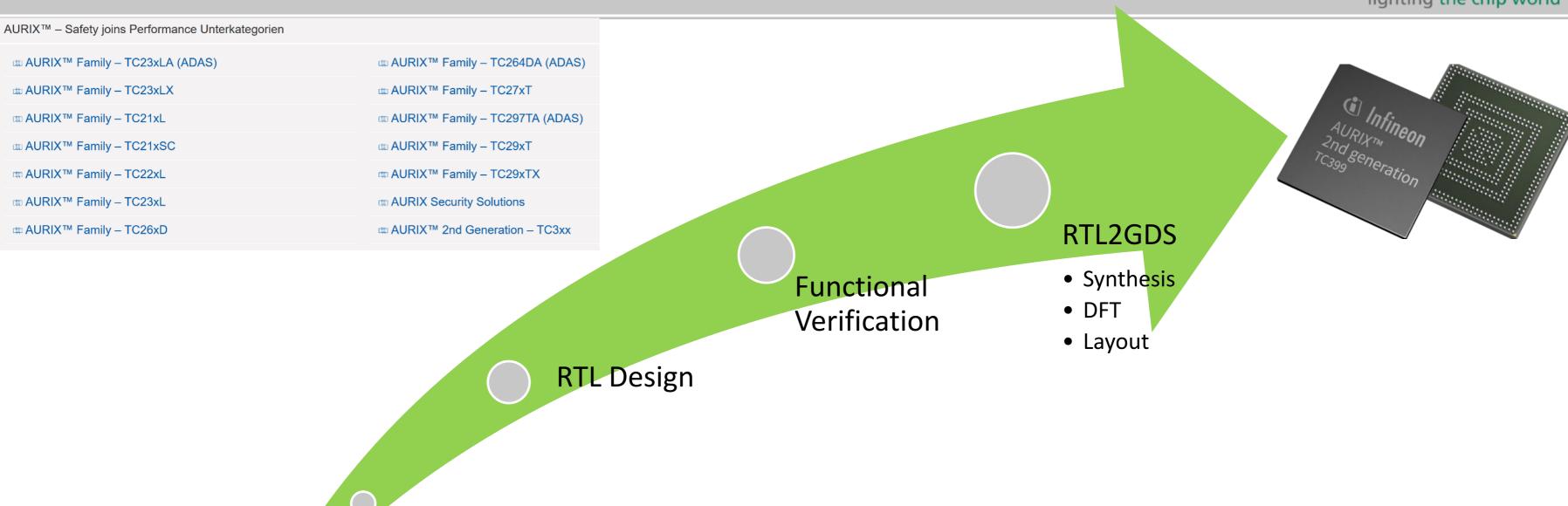

- ASIC /RTL2GDS & Functional Verification, RTL Design, Test

Engineering, Firmware, FPGA, and Embedded System development

from idea to prototype

- 15+ years of successful long-term project expertise and excellent QoR with Global Semiconductor Companies. Long term and good relationships in projects

- More than 100 senior experts

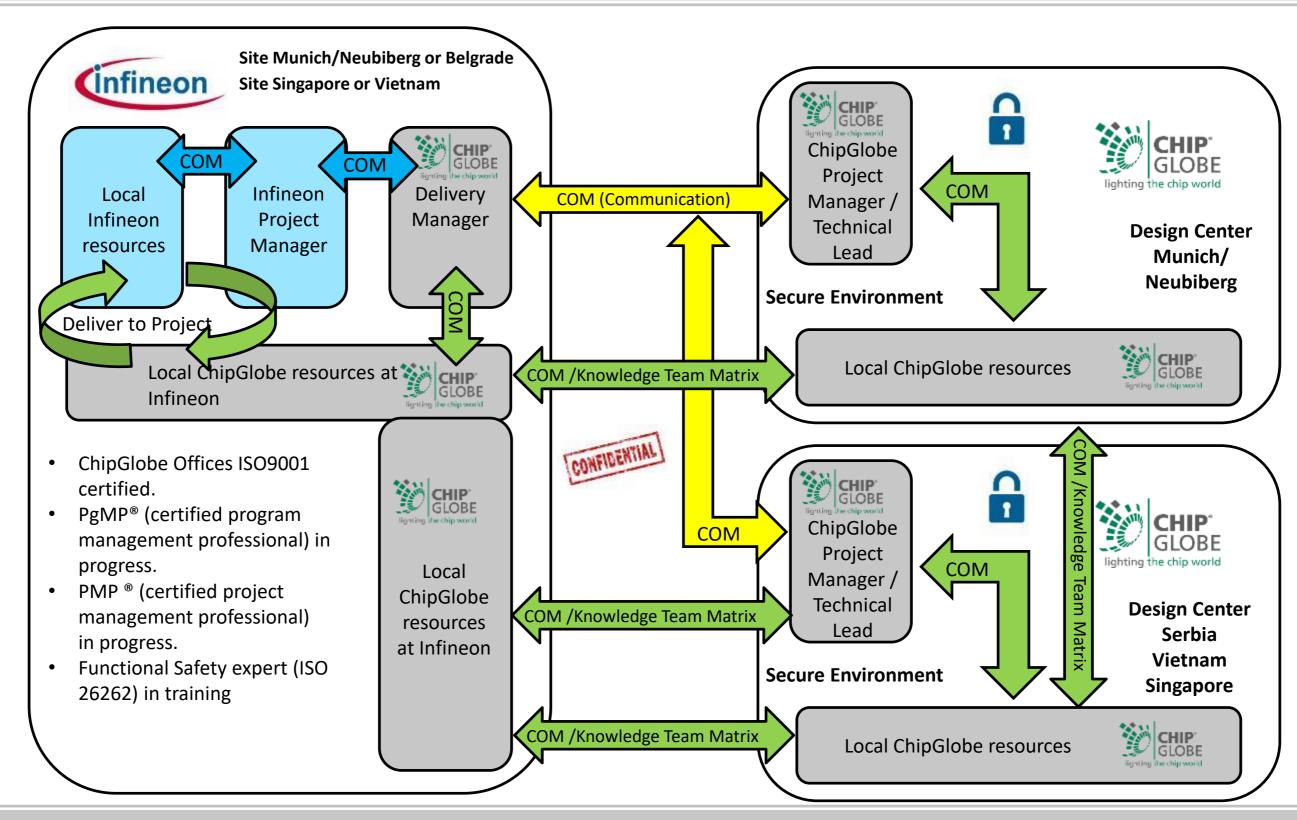

- Working successfully with our customers with ChipGlobe ODC

Model

- Embedded Systems Solution Provider: Infineon Security Partner

Network (ISPN) + Infineon Design House

### **Company Profile – Management Team**

# Diverse Management Team at ChipGlobe

Roland Klemt

Managing Director

ChipGlobe Germany GmbH

Volker Frisch CEO

Lay Suan Ng

Managing Director

ChipGlobe Asia Pacific Pte. Ltd.

Elizabeth Ngo

Managing Director

ChipGlobe Vietnam Co., Ltd.

Marija Ugarak

Managing Director

ChipGlobe d.o.o Beograd

&

ChipGlobe Greece MIKE

#### ChipGlobe GmbH

Cincinnatistrasse 60 81549 Munich, Germany Tel. +49 (89) 1222 469 0

www.ChipGlobe.com info@ChipGlobe.com

#### Office Address (ODC):

Professor-Messerschmitt-Strasse 1 85579 Neubiberg, Munich Germany

#### ChipGlobe Asia Pacific Pte. Ltd. (ODC)

25 International Business Park #04-64 German Centre Singapore 609916

#### ChipGlobe d.o.o Beograd (ODC)

Milutina Milankovića 11v 11070 Belgrade. Serbia GREEN HEART – Building N3, 5th floor

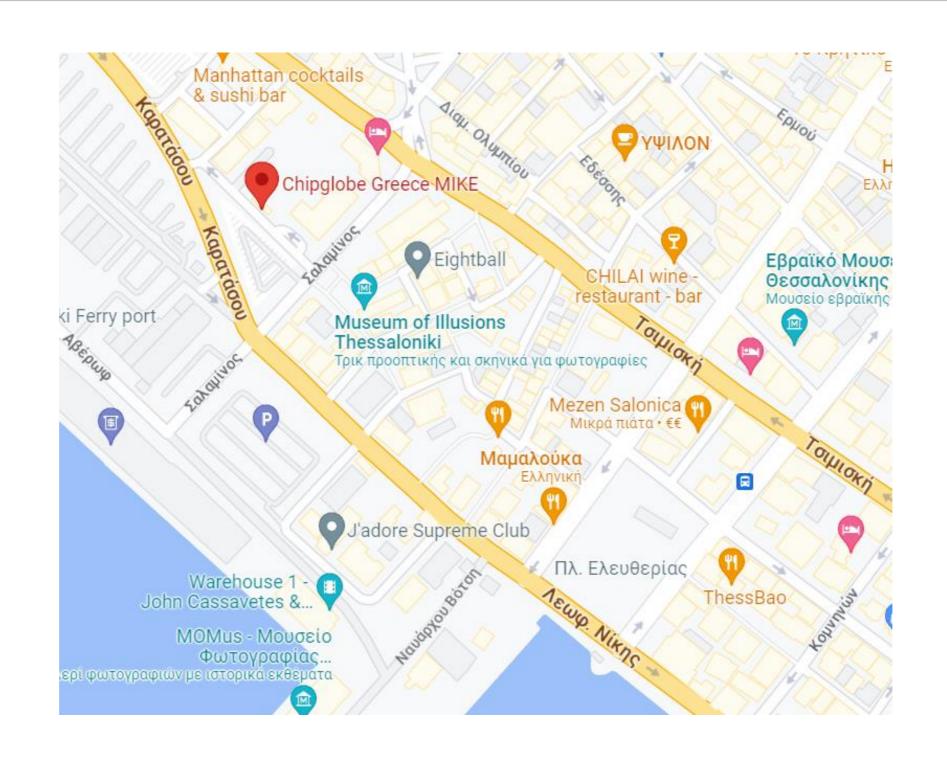

#### **ChipGlobe Greece MIKE (ODC)**

Karatasou 7 54626 Thessaloniki, Greece

#### ChipGlobe Vietnam Co., Ltd.

36/10 Nguyen Gia Tri Ward 25, Binh Thanh District Ho Chi Minh City Vietnam

### **ChipGlobe Locations & Focus Areas**

# **ChipGlobe Design Center Focus Areas**

| ODC - Neubiberg/Munich/Dresden - Germany |                                                                                                                         |  |  |  |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Now                                      | RTL2GDS, Funct. Verification, RTL Design,<br>Firmware, Analog Layout, DFT, Test Engineering<br>Program Management, FMEA |  |  |  |

| Roadmap                                  | RF, ISO26262 expert, PgMP®, PMP®                                                                                        |  |  |  |

| ODC – Singapore                          |                                                                                                                         |  |  |  |

| Now                                      | RTL2GDS, Functional Verification,<br>RTL Design, Program Management                                                     |  |  |  |

| ODC – Belgrade – Serbia                  |                                                                                                                         |  |  |  |

| Now                                      | Functional Verification, RTL Design, Firmware, TLM, Program Management, Application Boards, Mixed Signal Verification   |  |  |  |

| Roadmap                                  | RF, DFT, RTL2GDS,Tester Engineering                                                                                     |  |  |  |

| ODC – Ho Chi Minh, Vietnam               |                                                                                                                         |  |  |  |

| Now                                      | RTL2GDS, Functional Verification,<br>RTL Design, DFT, Firmware, Test Engineering                                        |  |  |  |

| ODC – Thessaloniki - Greece              |                                                                                                                         |  |  |  |

| Now                                      | Functional Verification, RTL Design, Mixed Signal Verification                                                          |  |  |  |

| Roadmap                                  | DFT, RTL2GDS,Tester Engineering                                                                                         |  |  |  |

### **ChipGlobe History**

### ChipGlobe d.o.o. Location and Track History of Success

- ChipGlobe ODC Belgrade opened in April 2017 with office space for 30 engineers.

- Moved to new office space in May 2020 space for 60 engineers.

- Successful Ramp up of the ODC aligned with Infineon and customer expectations.

- Focus: Functional Verification, RTL Design, Firmware Verification and Firmware/Embedded Systems Design

- Successful project involvement with Infineon in Munich and other global semiconductor companies in multiple projects

- Focus on senior and expert engineers.

- Internship program established + cooperation with technical university

Belgrade finalized to support the hiring of junior engineers

- Focus on Functional Verification and RTL Design in internships

ZERTIFIKAT

### ChipGlobe GmbH – ISO9001:2015 Qualification

## CERTIFICATE

The Certification Body of TÜV SÜD Management Service GmbH

certifies that

#### Chipglobe GmbH

site representative -

Cincinnatistr. 60, 81549 München Germany

at the site

Professor-Messerschmitt-Str. 1, 85579 Neubiberg

has established and applies a Quality Management System for

engineering services for customers in the area of System-on-Chip-Solutions.

An audit was performed, Order No. 707102988. Proof has been furnished that the requirements according to

#### ISO 9001:2015

are fulfilled.

The certificate is valid from 2020-01-03 until 2023-01-02. Certificate Registration No.: 12 100 59293 TMS

TOV SOD Management Service Gmb-1 \* Zentifizierungsstelle \* Ridlerstrasse 57 \* 80339 München \* Germany www.tuev-sued.de/cert\_icate-validity-check

As of Jan. 3, 2020, ChipGlobe GmbH is certified according ISO9001:2015 Quality Management System for

> "Provision of engineering services for customers in the area of System-on-Chip-Solutions"

www.tuev-sued.de/ms-zert

#### **ChipGlobe Focus Areas Technically**

- Working from ODCs in Munich, Belgrade, and Ho Chi Minh City – managed by ChipGlobe Onsite Manager

- Onsite sync meetings / ramp-up at customer sites

- Well-working teams enable large and complex tasks and designs

- Complementing major semiconductor companies' R&D teams

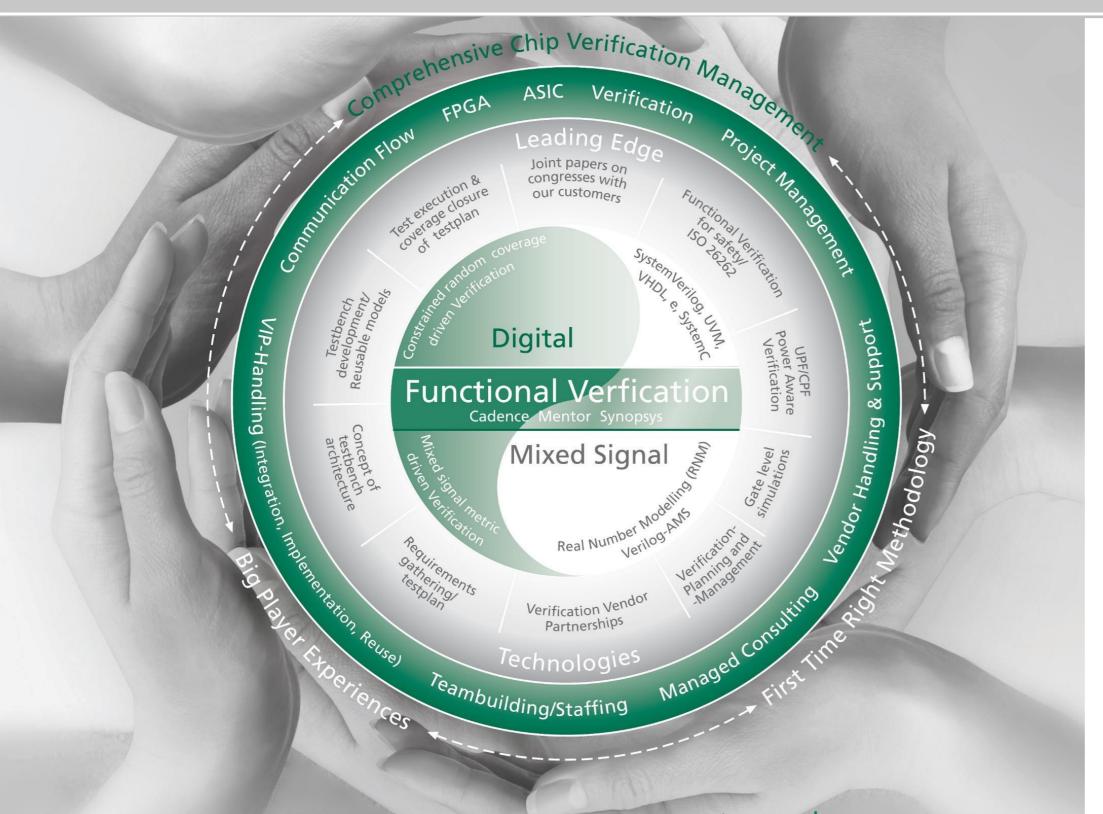

#### **Functional Verification**

- Broad and deep expertise in SystemVerilog and UVM

- From setup of testbench architecture to Module and Top Level Verification

- Proven Setup with Onsite Manager/Teamlead

@ customer site and setup with Offshore ODC teams and VPN integration.

### **Skillset Functional Verification Team**

|                            | Functional and Mixed Signal Verification                                                                                                                                                                                                                                                                                                                            |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Verification Languages     | <ul> <li>Specman e, eVC development</li> <li>System C, C++, TLM (Transaction Level Modelling)</li> <li>SystemVerilog / RNM (Real Number Modelling)</li> <li>Verilog</li> <li>Verilog-AMS</li> <li>VHDL</li> </ul>                                                                                                                                                   |

| Verification Methodologies | <ul> <li>Constraint random coverage driven verification</li> <li>Mixed signal metric driven verification</li> <li>SoC + IP level verification</li> <li>Gate level verification</li> <li>Firmware verification</li> <li>Portable stimulus (in rampup together with Mentor)</li> <li>Secure designs and verification based on ISO 26262</li> <li>UVM / OVM</li> </ul> |

| Power Aware Verification   | <ul> <li>CPF</li> <li>IEEE 1801 / UPF</li> <li>UPF low power verification</li> </ul>                                                                                                                                                                                                                                                                                |

| Verification Partnerships  | <ul> <li>Mentor Questa® Vanguard Partnership and Open Door Partnership Member</li> <li>Tool Independent Expertise in Projects with Cadence, Mentor + Synopsys Environments</li> </ul>                                                                                                                                                                               |

| EDA Vendor Tool            | Cadence, Mentor, Synopsys, JIRA and other bug/issue tracking tools                                                                                                                                                                                                                                                                                                  |

### **Different Levels and Approaches**

Our verification experts are always ready for the next challenge, whether it is a verification process starting from the device concept phase, defining and executing a methodology transition, or performing upgrades, maintenance, and support. Starting from the module level and all the way through to the SoC level of verification, we are offering structured and documented project execution providing limitless possibilities for re-use and upgrades in the next product cycles.

- Verification environment development/transition/upgrade

- > Test development, transition, and/or upgrade

- > 3<sup>rd</sup> party VIP usage and/or VIP development

- Metric-driven functional verification

- Coverage closure

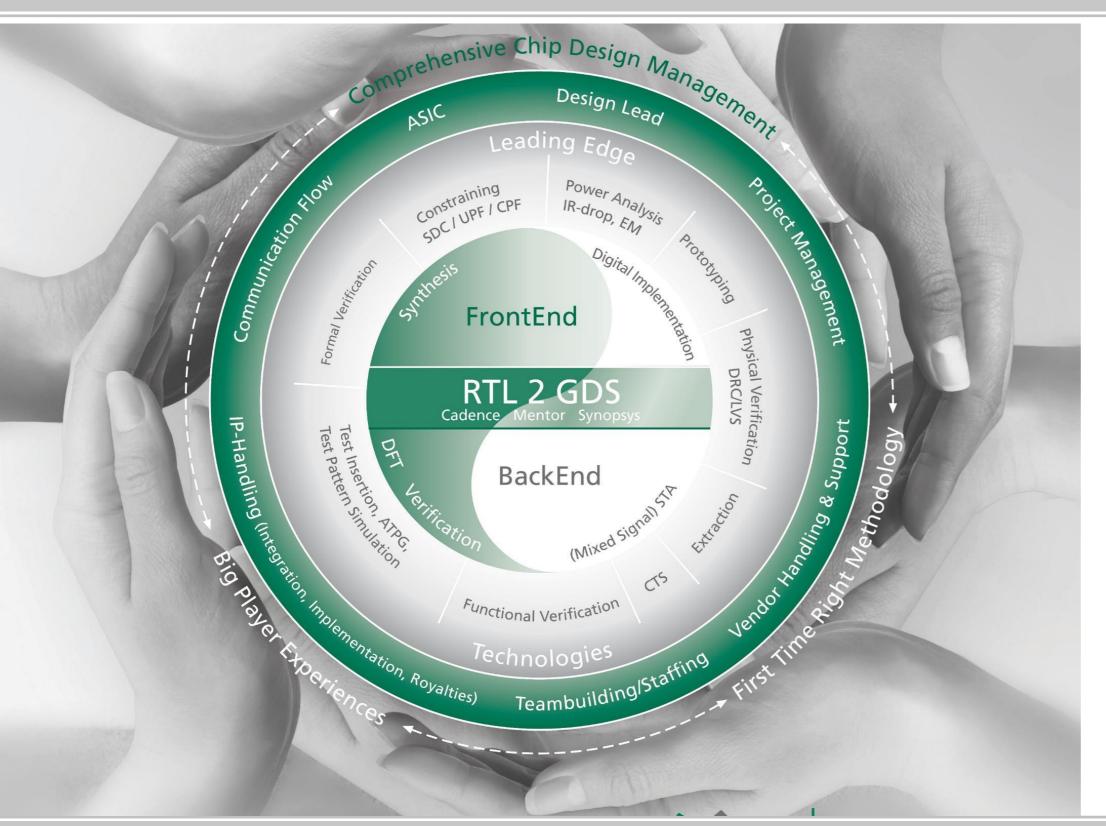

# **Skillset Design Service Team**

|                   | Design Service / RTL Design                                                                                                                                        |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Languages         | <ul> <li>VHDL</li> <li>Verilog</li> <li>SystemVerilog</li> <li>Perl, TCL, Makefile and Python scripting</li> </ul>                                                 |

| Design categories | <ul> <li>RTL design</li> <li>Lint, CDC and RDC checks</li> <li>Synthesis</li> <li>Logic equivalence checks (LEC)</li> <li>Functional safety (ISO 26262)</li> </ul> |

| EDA Vendor Tool   | <ul> <li>Cadence</li> <li>Synopsys</li> <li>Mentor</li> <li>JIRA and other bug/issue tracking tools</li> </ul>                                                     |

#### **Different Levels and Approaches**

- > Our design experts are always ready to share their experience and help to start from the device concept phase through defining safety mechanisms to the final sign-off timing closure phase.

- ➤ The optimal IP architectures and microarchitectures which save time during development and maintenance cycles are products of our experienced design engineers.

- > Our designers always take care of the trade-off against area, power, effort, and performance.

- ➤ Having experience in working on projects with various clients our design team offers support for design flow and methodology improvements.

- ➤ Last, but not least important, our designers provide structured and documented RTL designs with limitless possibilities for reuse and upgrades in the next product generations.

- ➤ Our digital design engineers have exceptional problem-solving and analytical skills and always look at the big picture. Moreover, they deal with their daily work in a pragmatic and enthusiastic way and communicate clearly and openly.

#### **RTL2GDS – Synthesis and Layout**

- Experience with 5nm,7nm, 14nm, 16nm, and 28 nm technology nodes

- Deep experience with Cadence + Synopsys

Flows /Tools + Mentor for DFT

# ChipGlobe Implementation – Design and Physical Verification (Tool independent expertize in projects for ANSYS, Cadence, Mentor Graphics and Synopsys environments)

| Specification                        | Vision                                                                                  |                                                                   |  |

|--------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------|--|

| RTL Coding                           | VHDL, Verilog, SystemVerilog                                                            |                                                                   |  |

| Linting, CDC Analysis                | Cadence® JasperGold ®, Incisive ® Enterprise Simulator (HAL), Conformal ®               | Constraint Designer                                               |  |

|                                      | Synopsys® SpyGlass®, SpyGlass® CDC                                                      |                                                                   |  |

| Synthesis                            | Cadence® Genus™ Synthesis (RTL Compiler), First Encounter®                              |                                                                   |  |

|                                      | Synopsys® Design Compiler®                                                              |                                                                   |  |

| STA (Top Level, hierarchical design, | Cadence® Tempus <sup>TM</sup>                                                           |                                                                   |  |

| macro level)                         | Synopsys® PrimeTime®, MSSTA (mixed signal)                                              |                                                                   |  |

| DfT, ATPG                            | Cadence® Genus™ (RTL Compiler), Modus™ test, Conformal®, Incisive® Enterprise Simulator |                                                                   |  |

|                                      | Mentor DFT Advisor, BSD Architect, MBISTArchitect™, LBISTArchitect™,                    |                                                                   |  |

|                                      | Graphics® Tessent® Testkompress®, Fastscan™, Modelsim®                                  |                                                                   |  |

|                                      | Synopsys® DFT Compiler/DFTMAX™, TetraMAX®, VCS®, TetraMAX® LBIST                        |                                                                   |  |

| Formal Verification                  | Cadence® Conformal® Equivalence Checker, Conformal® Low Power                           |                                                                   |  |

|                                      | Synopsys® Formality®                                                                    |                                                                   |  |

| Floorplanning                        | Cadence® First Encounter®                                                               |                                                                   |  |

|                                      | Synopsys® IC Compiler™(ICC)                                                             |                                                                   |  |

| Physical Implementation              | Cadence® Innovus™ (Encounter®)                                                          |                                                                   |  |

|                                      | Synopsys® IC Compiler™ (ICC, ICC2)                                                      |                                                                   |  |

| Extraction                           | Cadence® Quantus™ QRC                                                                   |                                                                   |  |

|                                      | Synopsys® Star-RCXT™                                                                    |                                                                   |  |

| Physical Verification (DRC, LVS)     | Cadence® Physical Verification System (PVS)                                             |                                                                   |  |

|                                      | Mentor Graphics® Calibre®                                                               |                                                                   |  |

|                                      | Synopsys® ICV / Hercules™                                                               |                                                                   |  |

| Power Analysis - Power Consumption,  | ANSYS® ANSYS® Redhawk™                                                                  |                                                                   |  |

| IR Drop Analysis, EM Analysis        | I I AMANCAY VAILLE!                                                                     | narks are owned by the respective the U.S. and/or other countries |  |

|                                      | Synopsys® Primerail                                                                     | the old unufor other countries                                    |  |

### **ChipGlobe Focus Embedded Design**

- Working from ODCs in Munich and Belgrade managed by ChipGlobe Onsite Manager

- Onsite sync meetings/ramp-up at customer sites

- Well-working teams enable large and complex tasks and designs

- ISPN Preferred Partner (Infineon Security Partner Network)

- Creation of customized demonstrator boxes with customer-specific hardware, software, and cloud integration (IoT, Security, Hardware Encryption, Sensors, AWS)

### **Skillset Firmware Team**

|                     | Design Service / RTL Design                                                                                                                                                                                                                                                                                                       |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Languages           | <ul> <li>Assembly languages</li> <li>C/C++</li> <li>Bash</li> <li>Python</li> <li>Java</li> <li>Makefile/Cmake</li> </ul>                                                                                                                                                                                                         |

| Embedded categories | <ul> <li>Analog/Digital/Rf module design</li> <li>Firmware Design</li> <li>Device drivers</li> <li>Board bring up</li> <li>Software stack development</li> <li>Yocto build system environment</li> <li>Embedded Linux customization and development</li> <li>Automotive software</li> <li>Security in embedded systems</li> </ul> |

| Tools               | <ul> <li>Eclipse based IDE</li> <li>JIRA and other bug/issue tracking tools</li> <li>Skilled in different software versioning tools</li> <li>Code review</li> <li>Altium, hardware design environment</li> <li>Measurement equipment expertise</li> </ul>                                                                         |

### **Different Levels and Approaches**

Our embedded experts are always ready for the next challenge. With years of experience in different industries and our skill set, we are at the forefront of embedded system innovations. Starting from specification, to the final turn-key embedded system design, we are following the latest technologies and using reliable tools and methodologies.

#### Our design principles are:

- > test driven development

- Clean high-quality code

- Design patterns

- > Strong team collaboration

### **ChipGlobe Automotive Aurix Family Involvement**

AURIXTM TRICORETM

Specification / Functional Safety

- Involvement in Germany, Europe, and Asia

- See also Infineon Reference

Sharing approved by Infineon

### **Proven Carefree Setup with ChipGlobe**

### ChipGlobe in the News - Forbes Asia – July / August 2018

fourth-largest economy, Germany rates and high consumer spending. At ness to customer feedback. the heart of that strength is Frankfurt, which is positioning itself as Europe's company in the semiconductor indusnext financial capital to replace London try, embodies this strategic and logical that its success came only by prioritizin the post-Brexit era.

financial sectors across Asia, includ-Finance Managing Director Hubertus of its success. Väth said.

biggest global brands, continues to as- Director Dieter Rudolf. sert its dominance over the German

72,000 euro, while Germany's is 40,000 the Germany has become synonymous to Bavaria," said Bavarian Chamber of

sectors in the region must work much shoring. If you look at places like Serbia, vestment. ■ closely together, according to Sasse.

In fact, Munich has already begun to diversify its economy beyond its traditional industrial sector and has ventured beyond Germany's national

"Business and success should always be people driven and not just technology driven. Locally and globally, communication, transparency, respect and care is key to everything. Doing cross-border business and building global companies requires passion, partnerships and most of all, people," CM-Equity Founder and CEO Michael Kott said.

Over the past decades, German

s Europe's leading economic gineering has become the benchmark you have a lower cost structure but still powerhouse and the world's across the globe. Many have attributed have quality talent. The same applies to this competitive edge to the ability of Vietnam. The long-term trend is to fohas shown the world its winning for- German companies to adapt quickly to cus on Asia and that's why we're openmula: strong investment, low interest market requirements and their open- ing a new ODC and investing there,"

ChipGlobe, a German consulting approach and combines it with a com- ing its customers. "We have close partnerships with mitment to the success of its customers.

ing close and cordial working relation- in 2014, ChipGlobe hires highly experi- ers first and how they are doing in serships with Tokyo and Singapore. And enced engineers who can design com-vicing their own customers," explained that is something which we are very pletely customizable solutions for its CEO Bill McDermott. happy about because we believe the clients. This mission forms ChipGlobe's With experience across 25 industries future belongs to Asia," Frankfurt Main corporate culture and is the foundation and operations in 193 countries, SAP

of Bavaria, home to some of the world's tem," stressed Business Development and the availability of predictive appli-

Asia early on, ChipGlobe set up a sub- "SAP is the one company that can "The GDP per capita of Munich is sidiary in Singapore in 2015. And after put it all together in a highly coheropening an outsource design center ent, altruistic, purpose-driven way," euro. And if you look at the figures from (ODC) in Belgrade in 2017, the com- McDermott said. the south of the country, this part of pany has begun construction of a new Looking ahead, Germany will contin-ODC in Ho Chi Minh City, Vietnam.

"We combine the strengths of and develop closer ties with the Asia-Commerce and Industry President German and Asian systems of quality, Pacific. With its robust financial sector, culture and values. If you look at the political stability and well-developed To maintain its leadership in Germany large companies in Germany, they try infrastructure, the country will continue and the world, the public and private to reduce costs, sometimes through off-

Rudolf added.

Software giant SAP is another south-

"We aim to look at business chal-Founded by Volker Frisch in Munich lenges through the eyes of our custom-

closes the gap between the application "You can only be successful if you of innovative technologies, such as ma-Aside from Frankfurt, the federal state have the right vision and value sys- chine learning and artificial intelligence, cations, process and insights that are in Detecting growth opportunities in value chains to drive up productivity.

ue to set the pace of European growth

ChipGlobe GmbH Cincinnatistrasse 60 81549 München Name Department Telephone Thomas Rühlicke IFAG DES SDF +49 89 234 27180

E-Mail Internet thomas.ruehlicke@infineon.com

ww.infineon.com

Your letter Our sign

02.07.2018

#### To Whom it may concern,

"ChipGlobe has been a reliable and trusted supplier of Infineon Technologies AG for more than 15 years and has contributed to many successful ASIC implementations. They have been working for Infineon in several projects in different Infineon business units. This has resulted in reduced costs and increased efficiency. The partnership with their high level experts is based on sustainability – keeping the project specific knowledge within the ChipGlobe Design Center and Infineon R&D. Setup with Infineon's R&D teams was driven by easy interaction – same time zone, short travel time for personal meetings and closely aligned processes. ChipGlobe experts were committed to flexibility and the ability to react quickly on changes in demand. Infineon is collaborating with ChipGlobe internationally with their offshore design centers in Europe, as well as for onsite services in Singapore. ChipGlobe has been working on Infineon's automotive chip developments for more than 10 years, especially on the proven worldwide design support for the AURIX family. Their expertise in RTL2GDS and verification contributed to timely and sustainable ASIC roll-outs."

Please contact us at any point should you have questions about this recommendation.

Thomas Rühlicke

(thomas.ruehlicke@infineon.com / Tel +49 89 234 27180)

Karl Breidenbach

(karl.breidenbach@infineon.com / Tel +49 89 234 26897)

#### Infineon Technologies AC

Postal Address D-81726 München Internet www.infineon.com Headquarters Am Campeon 1-15, D-85579 Neubiberg Phone +49 (0)89 234-0 Chairman of the Supervisory Board Dr. Eckart Sünner

Management Board Dr. Reinhard Ploss (CEO), Dominik Asam, Dr. Helmut Gassel, Jochen Hanebeck

Registered office Neubiberg Commercial Register Amtsgericht München HRB 126492

### Infineon reference for ChipGlobe

"ChipGlobe has been a reliable and trusted supplier for more than 15 years and has contributed to many successful ASIC implementations.

They have been working for Infineon on several projects in different Infineon business units. This has resulted in reduced costs and increased efficiency.

The partnership with their high-level experts is based on sustainability – keeping the project-specific knowledge within the ChipGlobe Design Center and Infineon R&D. Setup with Infineon's R&D teams was driven by easy interaction – same time zone, short travel time for personal meetings, and closely aligned processes. ChipGlobe experts were committed to flexibility and the ability to react quickly to changes in demand.

Infineon is collaborating with ChipGlobe internationally with their offshore design centers (ODCs) in Europe, as well as for onsite services in Singapore.

ChipGlobe has been working on Infineon's automotive chip developments for more than 10 years, especially on the proven worldwide design support for the AURIX family. Their expertise in RTL2GDS and verification contributed to timely and sustainable ASIC roll-outs."

#### **Infineon Supplier Award – November 2018**

# **ChipGlobe is Preferred Supplier** at Infineon

- Top QoR (Quality of Results)

- Excellent Delivery in Time

- Proven Sustainability

- Excellent Teamwork

- Great Flexibility

- 15+ years proven partnership

#### From left to right:

- Volker Buttermann, Senior Director Purchasing at Infineon Technologies AG

- Volker Frisch, CEO at ChipGlobe GmbH

- Thomas Rühlicke, Senior Director SoC Design and Methodology at Infineon Technologies AG

- Roland Klemt, Managing Director at ChipGlobe GmbH

### ODC Thessaloniki – In the city center and close to the port

#### **Next steps**

#### **ChipGlobe GmbH**

Cincinnatistrasse 60 81549 Munich, Germany Tel. +49 (89) 1222 469 0

www.ChipGlobe.com

#### Office Address (ODC):

Professor-Messerschmidt-Strasse 1a 85579 Neubiberg, Munich Germany

#### ChipGlobe Asia Pacific Pte. Ltd. (ODC)

25 International Business Park #04-64 German Centre Singapore 609916

#### ChipGlobe d.o.o Beograd (ODC)

Milutina Milankovića 11v 11070 Belgrade. Serbia GREEN HEART – Building N3, 5th floor

#### **ChipGlobe Greece MIKE (ODC)**

Karatasou 7 54626 Thessaloniki, Greece

#### ChipGlobe VIETNAM CO., LTD

36/10 Nguyen Gia Tri Ward 25, Binh Thanh District Ho Chi Minh City Vietnam